# SCG2500AI Synchronous Clock Generator

2111 Comprehensive Drive Aurora, Illinois 60505 Phone: 630-851-4722 Fax: 630-851-5040 www.conwin.com

#### **General Description**

The SCG2500AI is a mixed-signal phase lock loop generating CMOS outputs from an intrinsically low jitter voltage controlled crystal oscillator. The SCG2500AI is based on Connor-Winfield's SCG2500 series product line.

The SCG2500AI can lock to one of two possible reference inputs at 8 kHz that are selectable using one input select pin. The SCG2500AI has an improved filter compared to the SCG2500. The new filter allows the SCG2500AI to more closely track the selected input reference and lowers switching MTIEs.

The SCG2500AI provides 3 alarm outputs, Loss of Reference A, (LOR A) Loss of Reference B, (LOR B), and Loss of Lock, (LOL) as compared to the SCG2500's combined alarms. LOL alarm is active when the phase error exceeds 1us. Switching references within 100 ns will then comply with GR-253-CORE requirements. LOR A and LOR B independently monitor the input references. If Both references are lost the unit will go into Free Run automatically. When both references are lost, the unit should be forced into Free Run (pin 5 = 1). LOR A and LOR B can then be monitored until the references return. Refer to Table 6 for more operational details.

The reference output at 8 kHz is derived from the oscillator output. Phase alignment of the 8 kHz output to the input cannot be guaranteed with dual input units.

The package maximum dimensions are .780" x .830" x .350" on a six layer FR4 board with surface mount pins. Parts are assembled using high temperature solder to withstand surface mount reflow processes.

Tri-State is not available with this model.

#### **Features**

- Industrial Temperature Range (-40°- 85°C)

- Phase Locked Output Frequency Control

- Intrinsically Low Jitter Crystal Oscillator

- Two Selectable References @ 8 kHz

- Hitless Reference Switching

- 2 Independent Reference Monitors

- LOL Alarm Output

- Force Free Run Function

- Automatic Free Run Operation upon

loss of both references

- Input Duty Cycle Tolerant

- 3.3 Volt Power Supply

- Small Size: 0.78" x 0.83" x 0.35" maximum

- Surface Mount, DIL Package

| Quick Overview         |           |         |  |  |

|------------------------|-----------|---------|--|--|

| Ref_In Osc_Out Ref_Out |           | Ref_Out |  |  |

| 8 kHz                  | 19.44 MHz | 8 kHz   |  |  |

| 8 kHz                  | 51.84 MHz | 8 kHz   |  |  |

US Headquarters: 630-851-4722 European Headquarters: +353-61-472221

## **Absolute Maximum Rating**

| Table 1         |                      |         |         |         |       |       |

|-----------------|----------------------|---------|---------|---------|-------|-------|

| Symbol          | Parameter            | Minimum | Nominal | Maximum | Units | Notes |

| V <sub>cc</sub> | Power Supply Voltage | -0.5    | -       | +4.0    | Volts |       |

| V               | Input Voltage        | -0.5    | -       | +5.5    | Volts |       |

| T <sub>s</sub>  | Storage Temperature  | -65.0   | -       | +150.0  | °C    |       |

# **Operating Specifications**

| Table 2                                                                                                                                    |                                                                                                   |         |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------|

| Parameter                                                                                                                                  | Specifications                                                                                    | Notes   |

| Voltage                                                                                                                                    | 3.3V ±5%                                                                                          | 1.0     |

| Current                                                                                                                                    | 150 mA @ 3.46V                                                                                    |         |

| Input Frequency Ref 1 and Ref 2                                                                                                            | 8 kHz                                                                                             | 2.0     |

| Available Oscillator Output Frequencies                                                                                                    | 19.44 MHz, 51.84 MHz                                                                              |         |

| Reference Output                                                                                                                           | 8 kHz                                                                                             | 6.0     |

| Temperature Range                                                                                                                          | -40° to 85°C                                                                                      |         |

| Input Jitter Tolerance<br>(Jitter Frequencies ≥ 10 Hz)                                                                                     | ≥ 1us Typical                                                                                     |         |

| Jitter Bandwidth                                                                                                                           | < 10 Hz                                                                                           |         |

| Acquisition Time<br>from a 10ppm frequency step.<br>from a reference switch.<br>during start-up or from Free Run.<br>Time to LOL alarm off | Apprx. 1 sec. for frequency lock<br>< 1 sec. for phase lock<br>30 - 60 sec. for phase lock<br>TBD |         |

| Capture/Pull-In Range                                                                                                                      | ± 32 ppm Minimum                                                                                  |         |

| Output Duty Cycle                                                                                                                          | 45/55 % Min/Max @ 50% Level                                                                       |         |

| Output Rise and Fall Time                                                                                                                  | 3 nS @ 20% to 80% output level                                                                    |         |

| Output Load                                                                                                                                | 30 pF                                                                                             |         |

| Alarm                                                                                                                                      | LOR A, LOR B, LOL                                                                                 |         |

| Free Run Accuracy                                                                                                                          | ±20 ppm                                                                                           |         |

| Package                                                                                                                                    | Fr4 SM 0.78" x 0.83" x 0.350" (Maximum)                                                           |         |

| MTIE @ Synchronization Rearrangement                                                                                                       | GR-253-CORE, 1999 R5-136                                                                          | 4.0, 4. |

| Dynamic Offset                                                                                                                             | ± 40 ns                                                                                           | 9.0     |

|                                                                                                                                            |                                                                                                   |         |

Table 3

# Input and Output Characteristics

| Symbol           | Parameter                            | Minimum | Nominal | Maximum | Units | Notes   |

|------------------|--------------------------------------|---------|---------|---------|-------|---------|

| V <sub>IH</sub>  | High level input voltage             | 2.0     | -       | 5.5     | V     |         |

| V <sub>IL</sub>  | Low level input voltage              | 0       | -       | 0.8     | V     |         |

| T <sub>io</sub>  | I/O to output valid                  | -       | -       | 10      | nS    |         |

| C <sub>OUT</sub> | Output capacitance                   | -       | -       | 10      | pF    |         |

| V <sub>HO</sub>  | High level output voltage loh = -4mA | 2.40    | -       | -       | -     | Vcc Min |

| V <sub>IO</sub>  | Low Level output voltage lo1 = 8mA   | -       | -       | 0.4     | -     | Vcc Max |

| T <sub>IB</sub>  | Input reference signal pulse width   | 30      | -       | -       | nS    |         |

Preliminary Data Sheet #: SG071 Page 2 of 12 Rev: P00 Date: 03/07/03

### **Output Jitter Specifications**

| Frequency (MHz) | Jitter BW 10 Hz<br>pS (RMS) |            | SONET Jitter BW 12 kHz<br>pS (RMS) | z - 20 MHz<br>m UI |

|-----------------|-----------------------------|------------|------------------------------------|--------------------|

| 19.44           | 10 Тур.                     | 0.194 Тур. | 1 Max., 0.5 Typ.                   | 0.019 Max.         |

| 51.84           | 10 Тур.                     | 0.518 Тур. | 1 Max., 0.5 Typ.                   | 0.052 Max.         |

#### **Operational Table**

#### Table 5

Table 4

| INPUTS        |       |       | -                 | OUTPUTS              |         |     | -     |       |

|---------------|-------|-------|-------------------|----------------------|---------|-----|-------|-------|

| Select<br>A/B | Ref A | Ref B | Force<br>Free Run | Oscillator<br>Output | Ref Out | LOL | LOR A | LOR B |

| Х             | А     | Α     | 1                 | FR                   | FR      | 0   | 1     | 1     |

| Х             | NA    | Α     | 1                 | FR                   | FR      | 0   | 0     | 1     |

| Х             | А     | NA    | 1                 | FR                   | FR      | 0   | 1     | 0     |

| Х             | NA    | NA    | 0 **              | FR                   | FR      | 0   | 0     | 0     |

| 0             | А     | Α     | 0                 | RA                   | RA      | 1   | 1     | 1     |

| 0             | Α     | NA    | 0                 | RA                   | RA      | 1   | 1     | 0     |

| 0             | NA    | Α     | 0                 | U                    | U       | 0   | 0     | 1     |

| 1             | А     | Α     | 0                 | RB                   | RB      | 1   | 1     | 1     |

| 1             | NA    | Α     | 0                 | RB                   | RB      | 1   | 0     | 1     |

| 1             | А     | NA    | 0                 | U                    | U       | 0   | 1     | 0     |

Notes:

A = Active

NA = Not Active FR = Free Run

RA = Locked to Reference A

RB = Locked to Reference B

U = Unstable (See note 7)

X = Don't Care

\*\* See Note 8.0

#### NOTES:

1.0 Requires external regulation

- 2.0 Externally selectable via Input Select AB

- 3.0 From a 20 ppm offset in reference frequency

- 4.0 Entry into Free Run doesn't meet requirement for initial 2.33 seconds of self-timing

- 4.1 If the selected reference is removed, system response to the LOL ALARM must be less than 100ns

- 5.0 Upon power-up, allow 60 seconds for the SCG to obtain tight phase lock.

- 6.0 Static offset will accumulate with each reference switch for the Reference Output only.

- 7.0 Frequency will drift to lower limit rail if not switched.

- 8.0 Loss of both references will automatically force Free Run. Change the Force Free Run (pin 5) to 1 upon detection of this condition.

**9.0** Phase Drift from -40° to 85°C.

Preliminary Data Sheet #: SG071 Page 3 of 12 Rev: P00 Date: 03/07/03

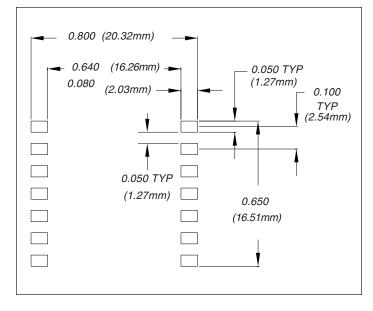

# **Circuit Board Footprint**

#### Figure 1

### **Pin Connections**

Table 6

| Pin | Connection                                     |

|-----|------------------------------------------------|

| 1   | Filtered 8 kHz Output                          |

| 2   | TCK (Do not connect, Factory use only)         |

| 3   | TMS (Do not connect, Factory use only)         |

| 4   | Ground                                         |

| 5   | Force Free Run / TDI (1 = Free Run)            |

| 6   | LOR A (1=Active Reference, 0=LOR)              |

| 7   | REF B                                          |

| 8   | REF A                                          |

| 9   | Oscillator Output                              |

| 10  | LOR B (1=Active Reference, 0=LOR)              |

| 11  | Vcc                                            |

| 12  | TDO (Do not connect, Factory use only)         |

| 13  | LOL of active reference (1=Locked, 0=Unlocked) |

| 14  | Input Reference Select AB (A = 0, B = 1)       |

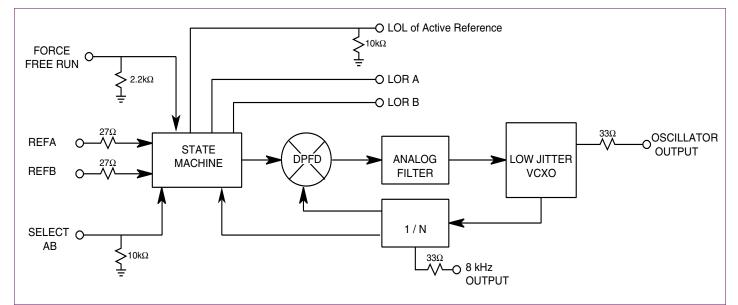

### **Block Diagram**

Figure 2

Preliminary Data Sheet #: SG071 Page 4 of 12 Rev: P00 Date: 03/07/03

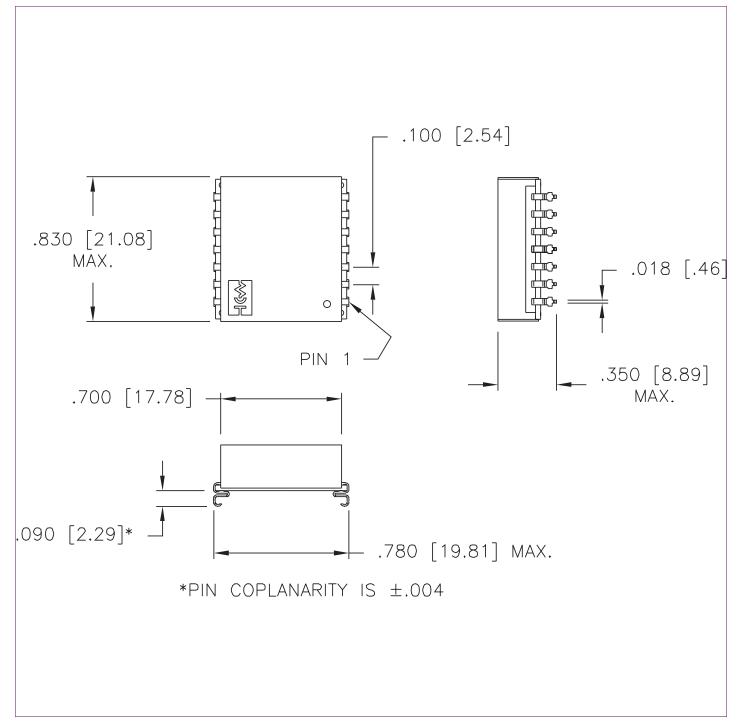

# Package Maximum Dimensions

Preliminary Data Sheet #: SG071 Page 5 of 12 Rev: P00 Date: 03/07/03

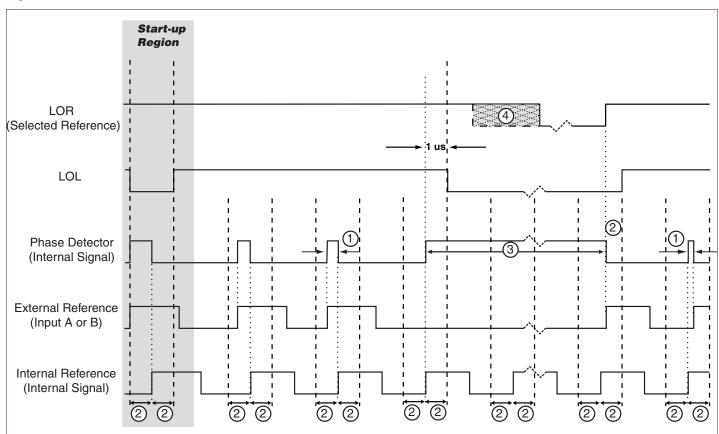

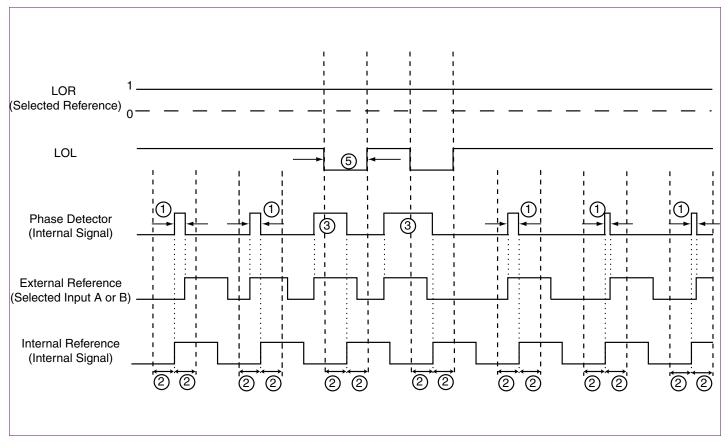

### LOR Alarm Diagram

#### AlarmTiming Legend Use for all alarm timing diagrams

Use for all alarm timing diagrams Table 7

|                 | 8 kHz Reference Input                                                          |

|-----------------|--------------------------------------------------------------------------------|

| 1               | < 1 µsec                                                                       |

| 2               | 1 μsec                                                                         |

| 3               | > 1 µsec                                                                       |

| 4               | 124 $\mu \text{sec}(\text{min})$ to 374 $\mu \text{sec}(\text{max})$ after LOL |

| 5               | Minimum pulse width = 2 $\mu$ s                                                |

| Start-up Region | During Start-up, The LOL Alarm will pulse                                      |

| Start-up negion | during the few seconds of operation                                            |

Preliminary Data Sheet #: SG071 Page 6 of 12 Rev: P00 Date: 03/07/03

**LOL Alarm Diagram**

Preliminary Data Sheet #: SG071 Page 7 of 12 Rev: P00 Date: 03/07/03

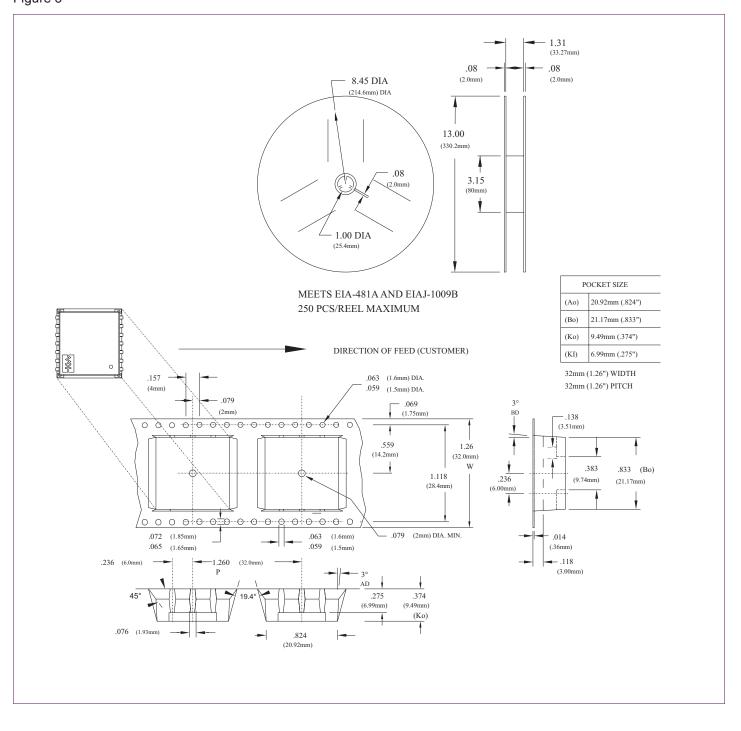

Tape and Reel Packaging Figure 6

Preliminary Data Sheet #: SG071 Page 8 of 12 Rev: P00 Date: 03/07/03

© Copyright 2003 The Connor-Winfield Corp. All Rights Reserved Specifications subject to change without notice

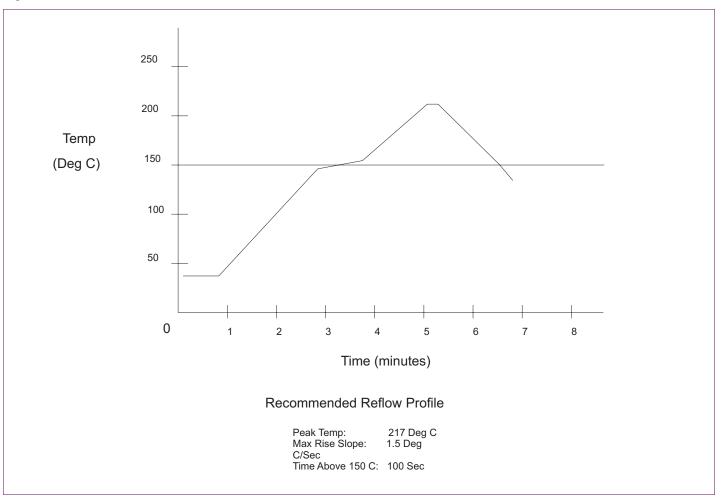

#### **Solder Profile**

Figure 7

# **Ordering Information**

SCG{XXXX}-{FFF.FFF}{M}

XXXX equals a specific model (2500AI) FFF.FFF equals the Oscillator Output frequency ( 019.44, 051.84, or 077.76 ) M equals MHz and is added to all part numbers

Example: To order an SCG2500AI with an Oscillator Output of 19.44 MHz, Order part number SCG2500AI-019.44M

Please contact Connor-Winfield for other frequencies that may be available.

Preliminary Data Sheet #: SG071 Page 9 of 12 Rev: P00 Date: 03/07/03

Preliminary Data Sheet #: SG071 Page 10 of 12 Rev: P00 Date: 03/07/03

© Copyright 2003 The Connor-Winfield Corp. All Rights Reserved Specifications subject to change without notice

Preliminary Data Sheet #: SG071 Page 11 of 12 Rev: P00 Date: 03/07/03

© Copyright 2003 The Connor-Winfield Corp. All Rights Reserved Specifications subject to change without notice

| Revision | Revision Date | Note                              |

|----------|---------------|-----------------------------------|

| P00      | 3/7/03        | Preliminary Informational Release |